## **AUSTRALASIAN UNIVERSITIES POWER ENGINEERING CONFERENCE**

VICTORIA UNIVERSITY, MELBOURNE, AUSTRALIA 10th - 13th DECEMBER, 2006 http://www.staff.vu.edu.au/aupec2006/

Reference number: 49

Dear Ali A-Ghadimi,

Your paper entitled "Detailed Modeling and analysis of a full bridge PWM DC-DC converter" has been fully peer reviewed by specialist national and/or international reviewers. On behalf of the Technical Committee, it is my pleasure to inform you that the paper has now been accepted for presentation at the Conference and for inclusion in the Conference Proceedings. We would like to invite you and your colleagues to participate in AUPEC 06 which is to be held in Melbourne, Australia from December 10 to 13, 2006.

Reviewer's reports are attached with this email. Please submit your revised paper to AUPEC06 technical secretariat by 16 October 06 addressing the questions/comments raised by the reviewers. If your paper does not require any changes based on the reviewers report, we will record your submitted full paper as the final paper for the conference.

Unless one of the authors of an accepted paper registers for the conference, the paper will not be published in the conference proceedings.

If you wish to present more than one paper at the conference, please note that a fee of \$100 per additional paper will be charged to cover the cost of inclusion in proceedings. The page limit is six pages per paper and any paper which exceeds this limit will be charged a page fee of \$100 per additional page.

The details on author's presentation guidelines will be available on the AUPEC'06 website shortly. Presenting authors are required to submit a brief biography (50-100 words) by 30<sup>th</sup> October, 2006 to the conference secretariat. Registration forms are available on the AUPEC'06 website at http://www.staff.vu.edu.au/aupec2006/registration.htm .

Accommodation information is available on the AUPEC'06 website http://www.staff.vu.edu.au/aupec2006/accomodation.htm . Please send any enquiries regarding your paper or the conference to amanullah.maungthanoo@research.vu.edu.au.

As December period is a busy period in Melbourne, it will be advisable to book accommodation at the earliest. The latest information on the conference including the programme will be posted on the conference homepage.

Kind regards.

Professor Akhtar Kalam General and Technical Chair

AUPEC 06

AUPEC 2006 Secretariat. Faculty of Health, Engineering and Science, PO BOX 14428, Melbourne VIC 8001 Australia, Phone: +61 3 9919 5504

Fax: 613 9919 4513 Mobile 0407 887964 Akhtar.kalam@vu.edu.au

# Detailed Modelling and Analysis of a Full Bridge PWM DC-DC Converter

Ali Asghar Ghadimi Abbas Molavi Daryani Hassan Rastegar

Department of Electrical Engineering Amirkabir University of Technology PO Box:15875 4413, Hafez Ave., Tehran, IRAN,

Email: ghadimi@aut.ac.ir abasmolavi@yahoo.com rastegar@ aut.ac.ir

#### **ABSTRACT**

This paper presents a detailed small-signal and transient analysis of a full bridge PWM converter designed for high voltage, high power applications using an average model. The derived model is implemented in a typical system and used to produce the small-signal and transient characteristics of the converter. Results obtained in the analysis of the high voltage and high power design example is validated by comparison for actual system with multiple switch and proposed model and show that the proposed model responses are identical to actual one and therefore the derived model can be used for performance analysis of the circuit and also design of controller.

## 1. Introduction

Today, new advances in power generation technologies and new environmental regulations encourage a significant increase of distributed generation resources around the world. Distributed generation systems (DGS) have mainly been used as a standby power source for critical businesses. For example, most hospitals and office buildings had stand-by diesel generators as an emergency power source for use only during outages. However, the diesel generators were not inherently costeffective, and produce noise and exhaust that would be objectionable on anything except for an emergency basis. On the other hand, environmental-friendly distributed generation systems such as fuel cells, micro turbines, biomass, wind turbines, hydro turbines or photovoltaic arrays can be a solution to meet both the increasing demand of electric power and environmental regulations due to green house gas emission [1-3]. Advances in power electronics and energy storage devices for transient backup have accelerate penetration of the distributed generation into electric power generation plants.

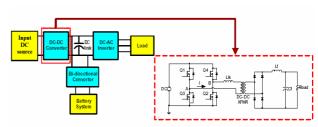

Most of this generation's unit has DC output and in order to produce higher AC voltage than the DC output voltage, they must have a DC/DC boost converter and a DC/AC inverter as shown in figure 1.

DC-DC converters can be used to boost and regulate low output voltage of any DC source like some new

distributed generation units to high voltage and compensate for its slow response during the transient. The main task of these converters is to maintain the output voltage at constant and predefined level.

Fig. 1: Block diagram of the power conversion system

To boost low voltage DC to high voltage DC a forward boost converter, a push-pull boost converter or an isolated full-bridge DC to DC power converter can be selected. Among these power converters, Full-Bridge converters are the most attractive topology for high power generation [4-6].

For control purpose and analyzing the behavior of converter, dynamic analysis of converter must be done. The choice of the average modeling method to study both large and small-signal characteristics of modern power converters has become widely accepted due to its adaptability to computer simulation. When an average model is simulated, it requires with less computation time than the switched circuit model [5]. Dynamic performance of some PWM dc-dc converters type has been analysed using state space averaging method in continues and discrete time domain [5-8].

In this paper, a large signal and small signal model of full-bridge dc-dc converter are studied. In this study, the parasitic resistances of switches are considered.

This paper is presented in seven sections. In Section 2, a discussion of Full-Bridge converter's operation is presented and in Section 3 the average model is described. The validity of derived model is verified by mean of simulation in section 4. Steady state analysis and dynamic model are in section 5, and in section 6 the proposed average model is validated by comparison to the switched circuit model. Finally in section 7, the conclusion of paper is presented.

#### 2. FULL-BRIDGE CONVERTER OPERATION

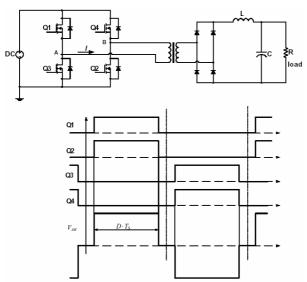

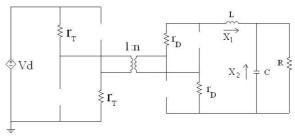

Figure 2 shows the circuit schematics of a full bridge converter that consist of a full bridge power converter (Q1 to Q4), a high frequency transformer (ratio 1:n), a bridge diode, and an output filter (L,C). The diagonally opposite switches (Q1 and Q2, or Q3 and Q4) are turned on and off simultaneously in a portion of each half cycle of switching frequency as shown in Figure 2 (for time interval D.T<sub>S</sub>. When all four switches are turned off, the load current freewheels through the rectifier diodes (for time interval T<sub>S</sub>/2-DT<sub>S</sub> [9].

Figure 2: operation of full bridge converter

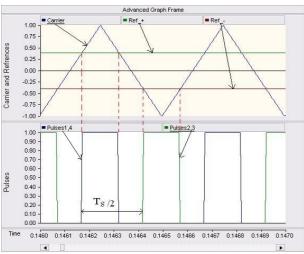

The PWM pulse generator has input of Duty Cycle (D) and will produces appropriate pulses and sends them to switches. Figure 3 shows signal waveform for producing appropriate pulses according to desired duty cycle (D).

Figure 3: PWM Generation for Full Bridge Converter

As shown in figure 3, a constant signal (Reference) is compared with a rectangular high frequency signal (Carrier). When carrier signal go over reference signal a pulse will produce and similarly negative value of reference signal will compare with carrier for producing other half cycle pulse. As shown in this figure by

changing reference signal from 0 to 1 we can have pulse with duty cycle of  $0.5*T_S$  to zero. This two pulse give to pair of switch and the switch will conduct in each half period with duration of  $DT_S$ .

In order to reduce the size and the weight of magnetic components, it is desirable to increase the switching frequency for DC-DC converters. However, when the switching frequency is increased, switching losses would increase, and snubbers and protection are required, which introduce significant losses and lower the efficiency.

## 3. DERIVING AVERAGED MODEL FOR FULL-BRIDGE CONVERTER

For modeling the full bridge converter and driving averaged model, it is assumed:

- 1- Transistor and diodes are identical

- 2- Transistors and diodes have on resistance  $r_T$ ,  $r_D$  respectively.

- 3- The output filter so designed that inductor current is continues in each switching period.

In this circuit, there is two state variable including capacitor voltage and inductor current.

As illustrated in previous section, full bridge converter has 2 mode of operation in each half cycle:

#### 3.1. MODE 1: $T_0 < T < T_{ON}$

In this mode, switches Q1 and Q2 are on and delivering energy to load via transformer and two diodes. For this mode, the circuit model is as shown in figure 4. Using KVL and KCL, we can derive the state equation of the circuit as presented below. In this model the state variable are inductance current  $(X_1)$  and capacitor voltage  $(X_2)$ :

$$KVL: \quad nV_d = R_{th}X_1 + L\dot{X}_1 + X_2$$

$$KCL: \quad X_1 = C\dot{X}_2 + \frac{X_2}{R}$$

$$where \quad R_{th} = 2n^2r_T + 2r_D$$

(1)

Figure 4: Mode 1 of operation

Therefore the state space model and matrices in the interval  $d.T_s$  are:

$$\dot{X} = A_1 X + B_1 V_d \qquad \quad , \qquad V_0 = C_1 X$$

$$A_{1} = \begin{bmatrix} -\frac{R_{th}}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix}$$

$$B_{1} = \begin{bmatrix} \frac{n}{L} \\ 0 \end{bmatrix}$$

$$C_{1} = \begin{bmatrix} 0 & 1 \end{bmatrix}$$

(2)

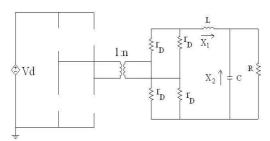

## 3.2. MODE 2: $T_{ON} < T < T_{S}/2$

In this mode, all switches are off and load current flow through bridge diodes and circuit can be modeled as figure 5.

Figure 5: Mode 2 of operation

Again there are following equation:

$$KVL: 0 = r_D X_1 + L\dot{X}_1 + X_2$$

$KCL: X_1 = C\dot{X}_2 + \frac{X_2}{R}$  (3)

And therefore state matrices in this mode are:

$$A_{2} = \begin{bmatrix} -\frac{r_{D}}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix} \qquad B_{1} = \begin{bmatrix} 0 \\ 0 \end{bmatrix} \qquad C_{1} = \begin{bmatrix} 0 & 1 \end{bmatrix}$$

(4)

Finally, based on averaged model concept [5,9], and because the last half cycle is identical to first half, we can obtain averaged model of this converter in Ts/2 as:

$$\dot{X} = AX + BV_d$$

,  $V_0 = CX$

$$A = A_1 2d + A_2 (1 - 2d) = \begin{bmatrix} -\frac{R_{th} 2d + r_D (1 - 2d)}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix}$$

(5)

$$B = B_1 2d + B_2 (1 - 2d) = \begin{bmatrix} \frac{2dn}{L} \\ 0 \end{bmatrix}$$

$$C = C_1 2d + C_2 (1 - 2d) = \begin{bmatrix} 0 \\ 1 \end{bmatrix}$$

This averaged model state equation can be used for simulation of converter instead of the model with multiple switches that may have long simulation time and also this state equation can used for analysis of original one performance and development of controller and stability studies.

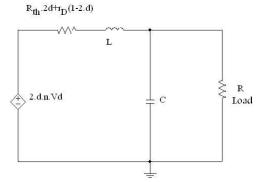

Based on above average model, the following electrical circuit model can be derived and used for simulation, design of controller, and stability studies.

Figure 6: Large signal averaged model of Full Bridge Converter

#### 4. MODEL VALIDATION

To validate the proposed method, we studied a 5 KW system with the parameter shown in table 1. PSCAd/EMTDC that is an industry standard simulation tool for studying the transient behavior of electrical networks [10] is used for simulation. In this study, the Output filter of the converter is so designed that there is 2% ripple in inductor current and 1% ripple in output voltage [11].

**Table 1: System Parameter**

| Input Voltage<br>Vd (Volts) | 50     | Filter Inductance<br>L (mH)           | 7    |

|-----------------------------|--------|---------------------------------------|------|

| Transformer<br>Power (KVA)  | 5      | Filter Capacitance<br>C (micro Farad) | 330  |

| Transformer<br>Voltages     | 50:500 | Load Resistance (ohms)                | 12.5 |

| Switching<br>Frequency (Hz) | 2000   | Switches on<br>Resistor (ohms)        | 5e-3 |

For verifying the proposed model, simulation with actual system and averaged model in large signal in 3 study cases performed:

#### 4.1. STEP CHANGE IN DUTY CYCLE (D)

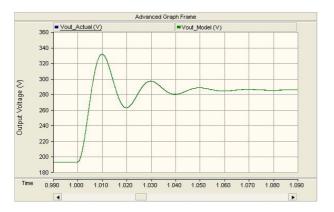

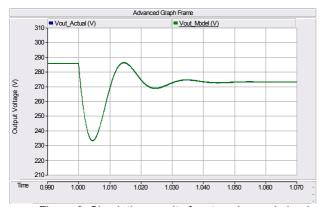

In this case the actual system and averaged model simulated with d=0.2 and then in time 1 seconds the duty cycle change from 0.2 to 0.3. Figure 7 shows the simulation results for this case and the actual model and actual result represented together for compare. Results show near perfect agreement, with the average model closely tracking those of the actual circuit and the model is valid in this large signal change in duty cycle (D).

Figure 7: Step change in duty cycle from 0.2 to 0.3 and output voltage in modelled system and actual one

#### 4.2. CHANGE IN LOAD

In this case a load transient from 100% to 50% full load is simulated at 1 second by turning off the load switch. Results from the transient simulation from both methods are shown superimposed in figure 8. As the figure shows, two waveforms are exactly identical and it is impossible to separate them. The figure also shows that output voltage drop when load is increased in this open loop system.

Figure 8: Simulation results for step change in load

#### 4.3. CHANGE IN INPUT VOLTAGE

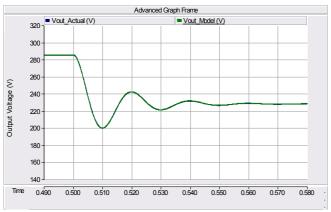

In final case study, a change in input voltage from 50 volts to 40 volts in time 0.5 sec. is simulated and the results show two waveforms are identical that means the output voltage is both model are identical.

Figure 9: Simulation waveform for step change in input voltage

#### 5. STEADY-STATE ANALYSIS

With the model of state space equation and matrices A,B,C we can consider small ac perturbation (represented by ~) and dc steady state (In upper case letters) quantities for model parameter as:

$$x = X + \widetilde{x}$$

$$v_o = V_o + \widetilde{v}_o$$

$$d = D + \widetilde{d}$$

$$v_d = V_d + \widetilde{v}_d$$

(6)

Substitution of this parameter into state equation (Eq. 5) vield:

$$\begin{split} \dot{\widetilde{x}} &= AX + BV_d + (A\widetilde{x} + B\widetilde{v}_d) + [(A_1 - A_2)X + (B_1 - B_2)V_d]2\widetilde{d} \\ &+ terms \ with \ product \ of \ \widetilde{x}, \widetilde{d}, \widetilde{v}_d (negligible) \end{split} \tag{7} \\ V_o + \widetilde{v}_o &= CX + C\widetilde{x} + [(C_1 - C_2)X]2\widetilde{d} \\ &+ terms \ with \ product \ of \ \widetilde{d}, \widetilde{v}_d (negligible) \end{split}$$

The steady state equation can be obtained from Eq. 7 by setting all ac components to zero. Therefore the steady state equation is:

$$AX + BV_d = 0$$

and for output:  $V_o = CX$  (8)

And therefore in Eq. 7 the small signal components have this relation:

$$\dot{\widetilde{x}} = A\widetilde{x} + B\widetilde{v}_d + [(A_1 - A_2)X + (B_1 - B_2)V_d]2\widetilde{d}$$

$$\widetilde{v}_o = C\widetilde{x} + [(C_1 - C_2)X]2\widetilde{d}$$

(9)

Using Eq. 8 and value of matrices in Eq. 5 the steady state dc voltage transfer function is:

$$m = \frac{V_o}{V_d} = -CA^{-1}B = 2Dn\frac{R}{R + R_{th}2D + r_D(1 - 2D)}$$

(10)

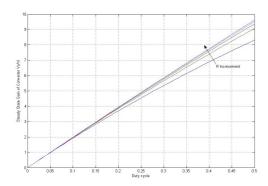

Figure 10 show the dc output to input gain (m) versus duty cycle (D) in several load resistance. As the figure shows there is approximately linear relationship between dc gain and duty cycle and as we increase D from 0 to 0.5 output voltage to input voltage gain will increase approximately in a linear manner.

From the curves, it is clear that an increase in load (by decreasing load resistance) result in a decreased gain for a constant duty cycle. Therefore, the steady state voltage must be regulated by changing duty cycle (D).

Figure 10: Steady state gain of converter in various Load resistance versus D

#### 6. SMALL SIGNAL ANALYSIS

From Eq. 9 that consists of ac perturbations and using laplace transform:

$$\widetilde{x}(s) = (SI - A)^{-1} [(A_1 - A_2)X + (B_1 - B_2)V_d] 2\widetilde{d}(s) + (SI - A)^{-1} B\widetilde{v}_d(s)$$

$$\widetilde{v}_o(s) = C\widetilde{x}(s) + [(C_1 - C_2)X] 2\widetilde{d}(s)$$

(11)

From Eq. 11 we can obtain output voltage laplace transform in term of input voltage and duty cycle:

$$\widetilde{v}_{o}(s) = \{C(SI - A)^{-1}[(A_{1} - A_{2})X + (B_{1} - B_{2})V_{d}] + (C_{1} - C_{2})X\}2\widetilde{d}(s) + C(SI - A)^{-1}B\widetilde{v}_{d}(s)$$

(12)

For obtaining transfer function of output voltage to duty cycle, the perturbation of input voltage is assumed to be zero and therefore:

$$\frac{\widetilde{v}_o(s)}{\widetilde{d}(s)} = 2C(SI - A)^{-1}[(A_1 - A_2)X + (B_1 - B_2)V_d] + 2(C_1 - C_2)X$$

(13)

Substituting matrices from Eq. 5 and simplification, the transfer function of Eq. 13 can be derived as Eq. 14:

$$\frac{\widetilde{v}_{o}(s)}{\widetilde{d}(s)} = \frac{2}{LC} \frac{nV_{d} + (r_{D} - R_{th})X_{1}}{den(s)}$$

Where:

$$den(s) = s^{2} + (\frac{1}{RC} + \frac{R'}{L})s + (\frac{R'}{RLC} + \frac{1}{LC})$$

and

$$R' = R_{th} 2D + r_{D}(1 - 2D)$$

(14)

$V_{\text{d}}$ , X1, D are steady state value for input voltage, inductance current and duty cycle respectively.

Based on the small signal model derived in previous section, it can be seen that the full bridge converter acts like a second order system. But as transfer function equation shows, dynamic of converter depend on operating point, since in the model inductor current and duty cycle steady state value of operating point exist.

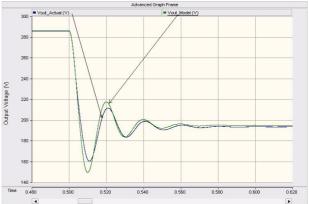

To validate the average model a step change in duty cycle (d from 0.3 to 0.28) has been introduced and the results are shown in figure 11.

Figure 11: Small signal model and actual model simulation for change 0.02 in d

Asshown in figure 11, the derived small signal response is very close to the switched circuit model; hence the transfer function can be used for dynamic analysis of the converter and designing controller.

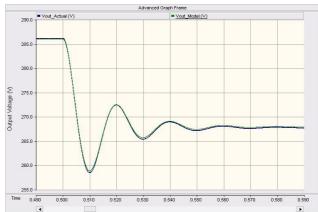

Another case is studied for a large change in duty cycle from 0.3 to 0.2, and result of voltage for this case is shown in figure 12. As figure show in this case the small signal model has a small difference with actual one but this difference is very small.

Figure 12: Small signal model and actual model simulation for change 0.1 in d

According to small-signal characteristics of this converter, compensation techniques for output voltage control are needed.

### 7. CONCLUSION

This paper presents an averaged model for full bridge dc-dc converter. The model used for steady state, dynamic analysis, and large signal analysis of this converter. The developed models are used to study the characteristics and dynamics of full bridge converter. The approach is applicable to simulation and controller design. Simulation results for the full bridge converter show the feasibility of the proposed model for steady-state analysis and small signal analysis and verify the derived model. Validation of the derived model is based on a comparison of dc, small-signal, and large-signal simulation results to those obtained from the simulation of the actual circuit.

#### REFERENCES

- [1]. M. N. Marwali and A. Keyhani, "Control of Distributed Generation Systems, Part I: Voltages and Currents Control," IEEE Transaction on Power Electronics, 2004.

- [2]. M. N. Marwali, J. W. Jung, and A. Keyhani, "Control of Distributed Generation Systems, Part II: Load Sharing Control," IEEE Transaction on Power Electronics, 2004

- [3]. A. A. Chowdhury, S. K. Agarwal, D. O. Koval, "Reliability modeling of distributed generation in conventional distribution systems planning and analysis," IEEE Transactions on Industry Applications, vol. 39, pp. 1493-1498, Sept.-Oct. 2003.

- [4]. J. W. Jung, and A. Keyhani, "Modeling and Control of Fuel Cell Based Distributed Generation Systems in a standalone Ac Power System", IAEE Journal, 2005

- [5]. Chris Iannello, Shiguo Luo, and Issa Batarseh, " Small-Signal and Transient Analysis of a Full-Bridge, Zero-Current-Switched PWM Converter Using an Average Model", IEEE Transaction on Power Electronics, Vol. 18, No. 3, 2003.

- [6]. Guinjoan, F.; Poveda, A.; Martinez, L.; Vicuna, L.G.; Majo, J., " An accurate small-signal modelling approach for switching DC-DC converters ", IEEE International Symposium on Circuits and Systems, 1993

- [7]. Piero G. Maranesi, Marco Riva," Automatic Modeling of PWM DC–DC Converters", IEEE Power Electronics Letters, Vol. 1, No. 4, 2003.

- [8]. Czarkowski, D.; Kazimierczuk, M.K., " SPICE compatible averaged models of PWM full-bridge DC-DC converter", Proceedings of the 1992 International Conference on Industrial Electronics, Control, Instrumentation, and Automation, 1992

- [9]. Mohan, Undeland, Robbins, "Power Electronics Converter. Application, and Design", third edition, wiley, 2003

- [10]. Anaya-Lara, O.; Acha, E., "Modeling and analysis of custom power systems by PSCAD/EMTDC ", IEEE Transactions on Power Delivery,2002

- [11]. A. Pressman, "Switching power Supply Design", Second edition, McGraw-Hill, 1998

- [12]. R. C. Dorf, R.H. Bishop, "Modern Control Systems", 9th Edition, 2000

- [13]. Marian K. Kazimierczuk and LaVern A. Starman, "Dynamic Performance of PWM DC-DC Boost Converter with Input Voltage Feedforward Control", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 46, NO. 12, DECEMBER 1999

- [14]. M. K. Kazimierczuk and A. Massarini, "Feedforward control of dc-dc PWM boost converter," IEEE Trans. Circuits Syst., I, vol. 44, pp. 143–148, Feb. 1997.

- [15]. B. Arbetter and D. Maksimovi'c, "Feedforward pulse width modulators for switching power converters," IEEE Trans. Power Electron., vol. 12, Mar. 1997.